# **NetVortex Data Sheet**

Lexra, Inc.

Release 1.9

April 2, 2001

Lexra Proprietary and Confidential

NetVortex Data Sheet Revision 1.3, for RTL Release 1.9.

This document is proprietary and confidential to Lexra, Inc. Copyright © 2001 Lexra, Inc. ALL RIGHTS RESERVED

MIPS, MIPS16, MIPS ABI, MIPSII, MIPSIV, MIPSV, MIPS32, R3000, R4000, and other MIPS common law marks are trademarks and/or registered trademarks of MIPS Technologies, Inc. Lexra, Inc. is not associated with MIPS Technologies, Inc. in any way.

SmoothCore, Radiax, and NetVortex are trademarks of Lexra, Inc.

# **Table of Contents**

| 1. | Net  | Vortex Product Overview                                                  | 9  |

|----|------|--------------------------------------------------------------------------|----|

|    | 1.1. | Introduction                                                             | 9  |

|    | 1.2. | Key Features                                                             | 10 |

|    | 1.3. | LX8000 Processor Overview                                                | 12 |

|    | 1.4. | NetVortex System Overview                                                | 14 |

|    | 1.5. | System Level Building Blocks                                             | 15 |

|    |      | 1.5.1. SMMU                                                              | 16 |

|    |      | 1.5.2. Local Memory Interface                                            | 16 |

|    |      | 1.5.3. Coprocessor Interface                                             |    |

|    |      | 1.5.4. Custom Engine Interface                                           | 16 |

|    |      | 1.5.5. Lexra Bus Controller                                              |    |

|    |      | 1.5.6. Block Transfer Controllers                                        | 17 |

|    |      | 1.5.7. Crossbar Device Interfaces                                        | 17 |

|    |      | 1.5.8. Device Management Interface                                       | 17 |

|    |      | 1.5.9. Building Block Integration                                        | 17 |

|    | 1.6. | RTL Core & SmoothCore                                                    | 17 |

|    | 1.7. | EDA Tool Support                                                         | 18 |

| 2. | LX8  | 0000 Architecture                                                        | 19 |

|    | 2.1. | Hardware Architecture                                                    |    |

|    | 2.1. | 2.1.1. Module Partitioning                                               |    |

|    |      | 2.1.1.       Module Full Holding         2.1.2.       Six Stage Pipeline |    |

|    | 2.2. | RALU Data Path                                                           |    |

|    | 2.2. | System Control Coprocessor (CP0)                                         |    |

|    | 2.4. | High-Performance Context Switch                                          |    |

|    |      | 2.4.1. New Context Registers                                             |    |

|    |      | 2.4.2. Reset                                                             |    |

|    |      | 2.4.3.       Determining the Number of Contexts in Software              |    |

|    |      | 2.4.4. Initiation of Context Switch                                      |    |

|    |      | 2.4.5. CSW Instruction                                                   |    |

|    |      | 2.4.6. LW.CSW, LT.CSW and LQ.CSW Instructions                            |    |

|    |      | 2.4.7. WD[.CSW] Instructions                                             |    |

|    |      | 2.4.8. WDLW.CSW, WDLT.CSW and WDLQ.CSW Instructions                      |    |

|    |      | 2.4.9. Pipeline                                                          |    |

|    |      | 2.4.10. New Thread Selection                                             |    |

|    |      | 2.4.11. Example Context Switch for Coprocessor Operation                 |    |

|    |      | 2.4.12. Program Access to New Registers                                  |    |

|    |      | 2.4.13. Exceptions                                                       |    |

|    | 2.5. | Low-Overhead Prioritized Interrupts                                      |    |

| 2  |      |                                                                          |    |

| 3. |      | 3000 RISC Programming Model                                              |    |

|    | 3.1. | Summary of MIPS-I Instructions                                           |    |

|    |      | 3.1.1. ALU Instructions                                                  |    |

|    |      | 3.1.2. Load and Store Instructions                                       |    |

|    |      | 3.1.3. Conditional Move Instructions                                     |    |

|    |      | 3.1.4. Branch and Jump Instructions                                      |    |

|    |      | 3.1.5. Control Instructions                                              |    |

|    |      | 3.1.6. Coprocessor Instructions                                          |    |

|    | 3.2. | Opcode Extension Using the Custom Engine Interface (CEI)                 | 35 |

# LEXRA

|                        |                                                                                                                                                       | 3.2.1. CEI Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                                                                   |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                                                       | 3.2.2. Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                                   |

|                        | 3.3.                                                                                                                                                  | Memory Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                   |

|                        | 3.4.                                                                                                                                                  | Exception Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

|                        |                                                                                                                                                       | 3.4.1. Exception Processing Registers: STATUS, CAUSE, EPC, BadVAddr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

|                        |                                                                                                                                                       | 3.4.2. Exception Processing: Entry and Exit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                      |

|                        | 3.5.                                                                                                                                                  | The Coprocessor Interface (CI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                                   |

| 4.                     | LX8                                                                                                                                                   | 000 Instruction Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                                                                   |

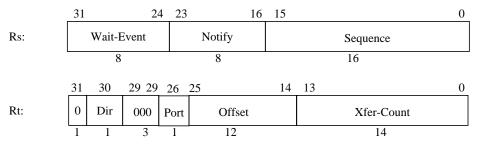

|                        | 4.1.                                                                                                                                                  | Context Switch and Data Transfer Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                                   |

|                        | 4.2.                                                                                                                                                  | Bit Field Processing Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                                                                                                   |

|                        | 4.3.                                                                                                                                                  | Cross Context Access Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

|                        | 4.4.                                                                                                                                                  | Checksum Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                                                                   |

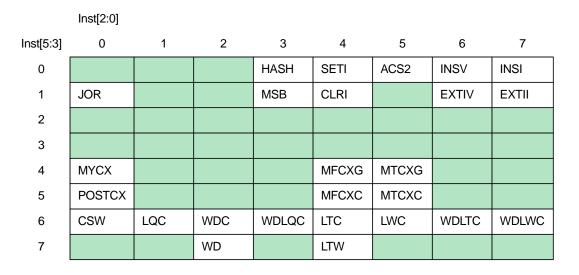

|                        | 4.5.                                                                                                                                                  | LX8000 Instruction Summary and Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.1. LX8000 Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.2. Load Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.3. Write Descriptor Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.4. Context, Checksum and Bit Field Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.5. Cross Context Move Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.6. Lexra-Coprocessor0 Register Access Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

|                        |                                                                                                                                                       | 4.5.7. Lexra SUBOP Bit Encodings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| 5.                     | LX8                                                                                                                                                   | 000 Local Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61                                                                                                                   |

|                        | 5.1.                                                                                                                                                  | Local Memory Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                                   |

|                        | 5.2.                                                                                                                                                  | Cache Control Register: CCTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

|                        | 5.3.                                                                                                                                                  | Instruction Memory (IMEM) LMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      |

|                        | 5.4.                                                                                                                                                  | Scratch Pad Data Memory (DMEM) LMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                                   |

|                        |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 6.                     | LX8                                                                                                                                                   | 000 Coprocessor Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65                                                                                                                   |

| 6.                     | <b>LX8</b><br>6.1.                                                                                                                                    | Attaching a Coprocessor Using the Coprocessor Interface (CI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65                                                                                                                   |

| 6.                     |                                                                                                                                                       | Attaching a Coprocessor Using the Coprocessor Interface (CI)<br>Coprocessor Interface (CI) Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65<br>65                                                                                                             |

| 6.                     | 6.1.<br>6.2.<br>6.3.                                                                                                                                  | Attaching a Coprocessor Using the Coprocessor Interface (CI)<br>Coprocessor Interface (CI) Signals<br>Coprocessor Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65<br>65<br>66                                                                                                       |

| 6.                     | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li></ul>                                                                                         | Attaching a Coprocessor Using the Coprocessor Interface (CI)<br>Coprocessor Interface (CI) Signals<br>Coprocessor Write Operations<br>Coprocessor Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65<br>65<br>66<br>66                                                                                                 |

| 6.                     | 6.1.<br>6.2.<br>6.3.                                                                                                                                  | Attaching a Coprocessor Using the Coprocessor Interface (CI)<br>Coprocessor Interface (CI) Signals<br>Coprocessor Write Operations<br>Coprocessor Read Operations<br>Coprocessor Interface and Pipeline Stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>65<br>66<br>66<br>67                                                                                           |

| 6.                     | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li></ul>                                                                                         | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65<br>65<br>66<br>66<br>67<br>67                                                                                     |

| 6.                     | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li></ul>                                                                                         | Attaching a Coprocessor Using the Coprocessor Interface (CI)<br>Coprocessor Interface (CI) Signals<br>Coprocessor Write Operations<br>Coprocessor Read Operations<br>Coprocessor Interface and Pipeline Stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65<br>65<br>66<br>66<br>67<br>67                                                                                     |

| <b>6.</b><br><b>7.</b> | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li><li>6.5.</li></ul>                                                                            | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65<br>65<br>66<br>66<br>67<br>67<br>67                                                                               |

|                        | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li><li>6.5.</li></ul>                                                                            | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65<br>65<br>66<br>67<br>67<br>67<br>67                                                                               |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul>                                                                      | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation         000 EJTAG         Introduction         Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>69<br>69                                                                   |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>69<br>69<br>70                                                             |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1.                                                             | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout         Single Processor PC Trace                                                                                                                                                                                                                                                                                                                                                                                                      | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>69<br>69<br>70<br>71                                                       |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1.       IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1.       PC Trace DCLK - Debug Clock                                                                                                                                                                                                                                                                                                                                   | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>69<br>69<br>70<br>71                                                 |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1.       IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1.       PC Trace DCLK - Debug Clock         7.3.2.       PC Trace PCST - Program Counter Status Trace                                                                                                                                                                                                                                                                 | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>69<br>69<br>70<br>71<br>71                                           |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1.       IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1.       PC Trace DCLK - Debug Clock         7.3.2.       PC Trace TPC - Target Program Counter                                                                                                                                                                                                                                                                        | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>69<br>69<br>70<br>71<br>71<br>71                                     |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1.       IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1.       PC Trace DCLK - Debug Clock         7.3.2.       PC Trace TPC - Target Program Counter         7.3.4.       Single-Processor PC Trace Pinout                                                                                                                                                                                                                  | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>72                                     |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1. PC Trace DCLK - Debug Clock         7.3.2. PC Trace PCST - Program Counter Status Trace         7.3.3. PC Trace TPC - Target Program Counter         7.3.4. Single-Processor PC Trace         7.3.5. Vectored Interrupts and PC Trace                                                                                                                                                 | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>72<br>72                               |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>LX8</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> </ul>               | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1. PC Trace DCLK - Debug Clock         7.3.2. PC Trace PCST - Program Counter Status Trace         7.3.3. PC Trace TPC - Target Program Counter         7.3.4. Single-Processor PC Trace         7.3.5. Vectored Interrupts and PC Trace         7.3.6. Demultiplexing of TDO and TDI During PC Trace                                                                                    | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>69<br>70<br>71<br>71<br>71<br>71<br>72<br>72<br>73             |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul> LX8 7.1. 7.2.                                                        | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1.       IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1.       PC Trace DCLK - Debug Clock         7.3.2.       PC Trace PCST - Program Counter Status Trace         7.3.3.       PC Trace TPC - Target Program Counter         7.3.4.       Single-Processor PC Trace         7.3.5.       Vectored Interrupts and PC Trace         7.3.6.       Demultiplexing of TDO and TDI During PC Trace         Multiprocessor EJTAG | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>71<br>72<br>73<br>73                   |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>LX8</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> </ul>               | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1. PC Trace DCLK - Debug Clock         7.3.2. PC Trace PCST - Program Counter Status Trace         7.3.3. PC Trace TPC - Target Program Counter         7.3.4. Single-Processor PC Trace         7.3.5. Vectored Interrupts and PC Trace         7.3.6. Demultiplexing of TDO and TDI During PC Trace         Multiprocessor EJTAG         7.4.1. Connectivity Requirements              | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>71<br>71<br>72<br>72<br>73<br>73       |

| 7.                     | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>LX8</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> </ul> | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1.       Pipeline Holds         6.5.2.       Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>71<br>72<br>73<br>73<br>73       |

|                        | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>LX8</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> </ul> | Attaching a Coprocessor Using the Coprocessor Interface (CI)         Coprocessor Interface (CI) Signals         Coprocessor Write Operations         Coprocessor Read Operations         Coprocessor Interface and Pipeline Stages         6.5.1. Pipeline Holds         6.5.2. Pipeline Invalidation <b>000 EJTAG</b> Introduction         Overview         7.2.1. IEEE JTAG-specific Pinout         Single Processor PC Trace         7.3.1. PC Trace DCLK - Debug Clock         7.3.2. PC Trace PCST - Program Counter Status Trace         7.3.3. PC Trace TPC - Target Program Counter         7.3.4. Single-Processor PC Trace         7.3.5. Vectored Interrupts and PC Trace         7.3.6. Demultiplexing of TDO and TDI During PC Trace         Multiprocessor EJTAG         7.4.1. Connectivity Requirements              | 65<br>65<br>66<br>67<br>67<br>67<br>67<br>67<br>67<br>71<br>71<br>71<br>71<br>71<br>71<br>72<br>73<br>73<br>73<br>73 |

#### **NetVortex**

| LEXT  | April 2, 2001                                | Ne |

|-------|----------------------------------------------|----|

| 8.2.  | Device-to-Processor Paths                    |    |

| 8.3.  | Bandwidth and Latency                        |    |

| 8.4.  | Crossbar Port Configuration                  |    |

| 8.5.  | Address Decoding                             |    |

|       | 8.5.1. Memory Mapped Devices                 |    |

|       | 8.5.2. Write Descriptor Devices              |    |

|       | 8.5.3. Address Error Handling                |    |

| 8.6.  | Arbitration                                  |    |

| 8.7.  | Asynchronous Interface                       |    |

| 8.8.  | Queue Depths                                 |    |

| 8.9.  | Instruction RAM Fill                         |    |

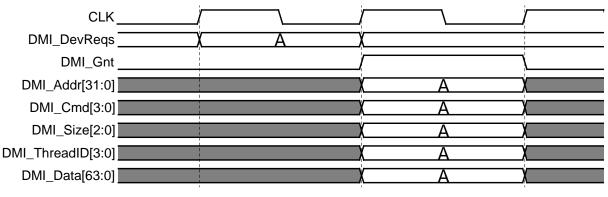

| 8.10. | Device Management Interface                  |    |

|       | 8.10.1. DMI Read and Write Request Interface |    |

|       | 8.10.2. DMI Request Waveforms                |    |

|       | 8.10.3. DMI Split Read Data Interface        |    |

|       | 8.10.4. DMI Read Data Waveforms              |    |

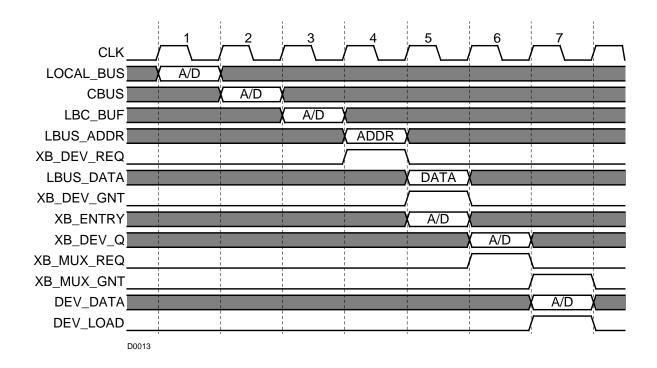

|       |       | 8.11.2. Device Request Waveforms                               |     |

|-------|-------|----------------------------------------------------------------|-----|

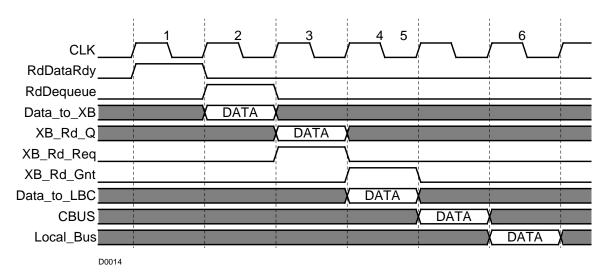

|       |       | 8.11.3. Device Read Data Interface                             |     |

|       |       | 8.11.4. Device Read Data Waveforms                             |     |

| 9. I  | NetV  | ortex Test and Set Engine                                      | 95  |

| 9     | ə.1.  | Semaphore Addressing                                           | 95  |

| 9     | Э.2.  | Single Word Read — Basic Test and Set                          | 95  |

| 9     | 9.3.  | Single Word Split-Read — (Enqueue and) Wait for Semaphore Free | 95  |

| 9     | 9.4.  | Single Word Write — (Dequeue Wait or) Clear Semaphore          | 95  |

| 9     | Э.5.  | RAM Requirements for Semaphore Queues                          | 96  |

| 9     | 9.6.  | Semaphore Usage for Critical Code Section                      | 96  |

| ç     | 9.7.  | Semaphore Usage for Cross Processor Wait and Post              | 97  |

| 9     | 9.8.  | Initialization                                                 |     |

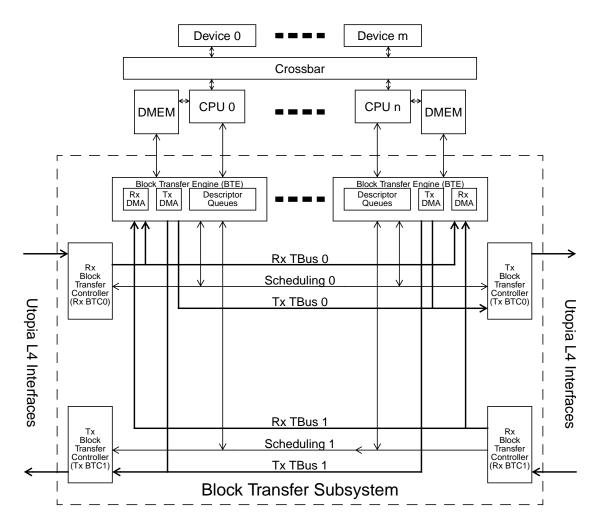

| 10. ľ | NetV  | ortex Block Transfer Subsystem                                 | 99  |

| 1     | 10.1. | Overview                                                       |     |

| 1     | 10.2. | Block Transfer Buffers and Transfer Descriptors                | 100 |

| 1     | 10.3. | Example Transaction Flow                                       | 102 |

| 1     | 10.4. | Detailed Description of Block Transfer Modules                 | 103 |

|       |       | 10.4.1. Block Transfer Engine                                  | 103 |

|       |       | 10.4.2. Rx and Tx Block Transfer Controllers                   |     |

8.11 Direct FIFO Interface for Devices 88

#### Appendix A.NetVortex Lconfig Forms .....107 A.1. A.2. Packet Processor Unit 107 A.3. A.4. A.5. A.6. A.7. A.8. A.9.

| A.12.    | Configuration Options for the Test & Set Engine    |

|----------|----------------------------------------------------|

| A.13.    | Configuration Options for Write-Descriptor Devices |

| A.14.    | Configuration Options for the Crossbar114          |

| Appendix | x B.NetVortex Port Descriptions115                 |

| Appendix | x C. LX8000 Pipeline Stalls127                     |

| C.1.     | Stall Definitions                                  |

| C.2.     | Instruction Groupings                              |

| C.3.     | Non-Sequential Program Flow Issue Stall            |

| C.4.     | Load Subword Stall                                 |

| C.5.     | Store-Load Stall                                   |

| C.6.     | StoreAny - StoreSubword Stall                      |

| C.7.     | Load/Store Ops Stall Matrix                        |

| C.8.     | MVCz Stall                                         |

| C.9.     | IMMU Stall                                         |

| C.10.    | IMMU Issue Stall                                   |

| C.11.    | Icache Miss Stall                                  |

|          | Dcache Miss Stall                                  |

| C.13.    | Pipeline Timing Diagrams for Stalls                |

|          | C.13.1. Non-Sequential Program Flow Issue Stalls   |

|          | C.13.2. Load Subword Stall                         |

|          | C.13.3. Store-Load Stall                           |

|          | C.13.4. StoreAny - Store Subword Stall             |

|          | C.13.5. MVCz Stall                                 |

|          | C.13.6. LWCz Stall                                 |

|          | C.13.7. Icache Miss Stall                          |

|          | C.13.8. Dcache Miss Stall                          |

# **List of Tables**

| Table 1:  | EDA Tool Support                             | .18  |

|-----------|----------------------------------------------|------|

| Table 2:  | CP0 Registers                                | .21  |

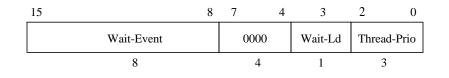

| Table 3:  | Context Status Register Detail               |      |

| Table 4:  | Scheduler Ports                              | . 27 |

| Table 5:  | Prioritized Interrupt Exception Vectors      |      |

| Table 6:  | ALU Instructions                             |      |

| Table 7:  | Load and Store Instructions                  |      |

| Table 8:  | Conditional Move Instructions                | . 33 |

| Table 9:  | Branch and Jump Instructions                 | . 33 |

| Table 10: | Control Instructions                         | . 34 |

| Table 11: | Coprocessor Instructions                     | . 35 |

| Table 12: | Custom Engine Interface Operations           | . 36 |

| Table 13: | Custom Engine Interface Signals              | . 36 |

| Table 14: | SMMU Address Mapping                         | . 37 |

| Table 15: | List of Exceptions                           | . 38 |

| Table 16: | Context Switching Instructions               | .41  |

| Table 17: | Bit Field Processing Instructions            | .45  |

| Table 18: | Hash Instruction Key Bit Definition          | . 50 |

| Table 19: | Cross Context Access Instructions            | . 52 |

| Table 20: | Checksum Addition Instructions               | . 53 |

| Table 21: | Instruction Summary                          | . 54 |

| Table 22: | Lexra SUBOP Bit Encoding                     | . 60 |

| Table 23: | Local Memory Interface Modules               | .61  |

| Table 24: | IMEM Configurations                          | . 62 |

| Table 25: | IMEM RAM Interfaces                          | . 63 |

| Table 26: | DMEM Configurations                          | . 63 |

| Table 27: | DMEM RAM Interfaces                          | . 64 |

| Table 28: | Coprocessor Interface Signals                | . 65 |

| Table 29: | EJTAG Pinout                                 |      |

| Table 30: | EJTAG AC Characteristics                     | .70  |

| Table 31: | EJTAG Synthesis Constraints                  |      |

| Table 32: | Single-Processor PC Trace Pinout.            |      |

| Table 33: | Single-Processor PC Trace AC Characteristics |      |

| Table 35: | DMI Request Signals                          |      |

| Table 36: | DMI Split Read Data Signals                  |      |

| Table 37: | Device Request Signals                       |      |

| Table 38: | Device Read Data Signals                     | .91  |

| Table 39: | Semaphore Engine RAM Requirements            |      |

| Table 40: | Block Transfer Descriptor                    |      |

| Table 41: | BTC Reserved Fields in Transfer Buffer       |      |

| Table 42: | Receive Port Signals                         |      |

| Table 44: | Lconfig Block Types                          |      |

| Table 45: | Memory Mapped Device Address Masks           |      |

| Table 46: | NetVortex Top Level Port Summary             |      |

| Table 47: | LX8000 Single-Processor Port Summary         |      |

| Table 48: | Instruction Groupings For Stall Definition   |      |

| Table 49: | Load/Store Ops Stall Matrix                  | 128  |

# **List of Figures**

| Figure 1:  | NetVortex LX8000 Processor Overview                              | 13 |

|------------|------------------------------------------------------------------|----|

| Figure 2:  | NetVortex System Overview                                        | 14 |

| Figure 3:  | Processor Core Module Partitioning                               | 19 |

| Figure 4:  | Context Associated Registers                                     |    |

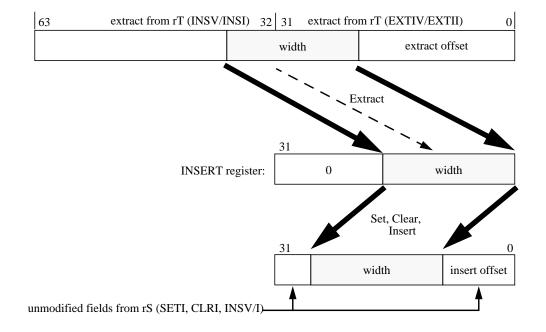

| Figure 5:  | Insert and Extract Operations (Straddle Case)                    | 45 |

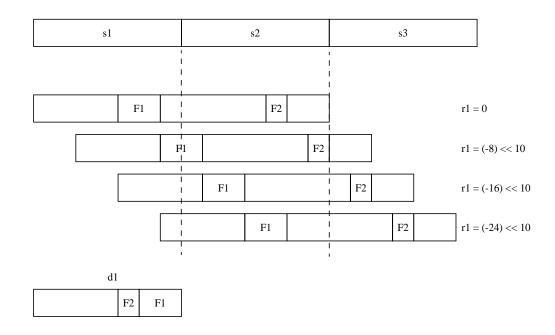

| Figure 6:  | Packet Field Compaction with Variable Alignment                  | 49 |

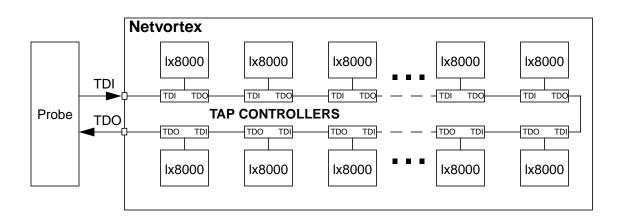

| Figure 7:  | Construction of Chained TAP controllers for Multiprocessor EJTAG | 73 |

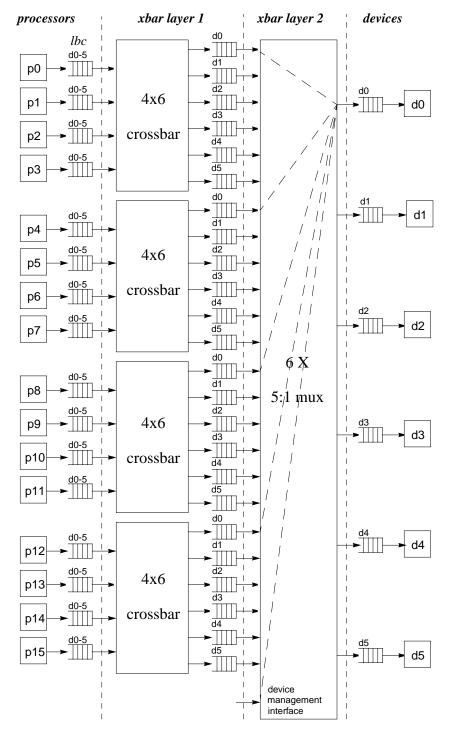

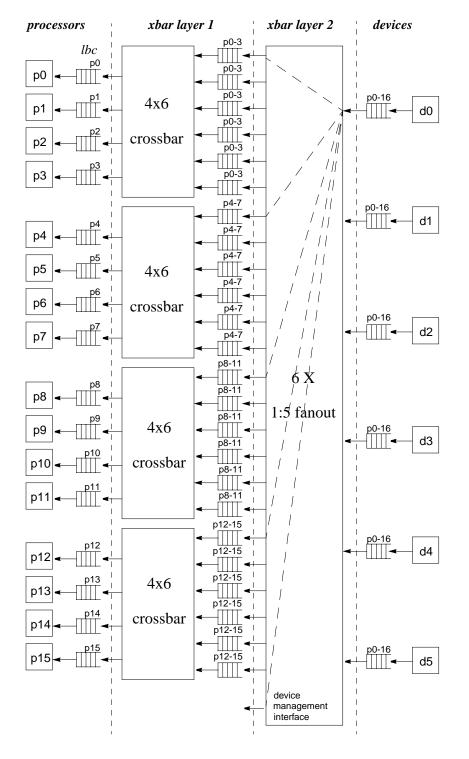

| Figure 8:  | Crossbar for 16 Processors and DMI to 6 Devices                  | 77 |

| Figure 9:  | Crossbar for 6 Devices to 16 Processors and DMI                  | 79 |

| Figure 10: | Processor to Device Transaction Flow                             | 80 |

| Figure 11: | Device to Processor Transaction Flow                             | 81 |

| Figure 12: | Single DMI Request Without Grant Delay                           | 85 |

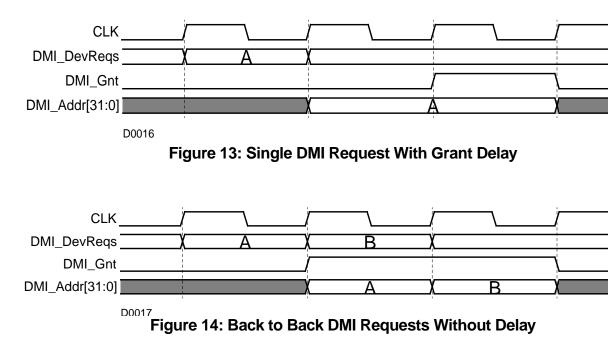

| Figure 13: | Single DMI Request With Grant Delay                              | 86 |

| Figure 14: | Back to Back DMI Requests Without Delay                          | 86 |

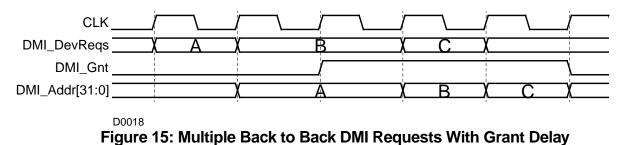

| Figure 15: | Multiple Back to Back DMI Requests With Grant Delay              | 86 |

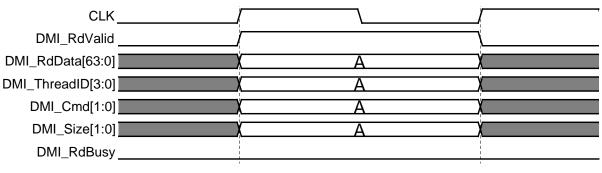

| Figure 16: | Single DMI Read Data Response Without Delay                      | 87 |

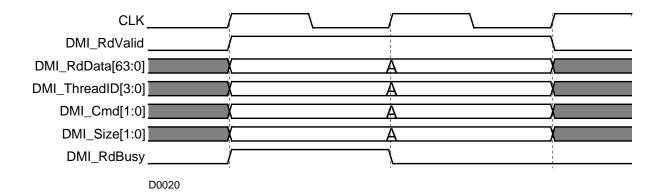

| Figure 17: | Single DMI Read Data Response With Busy Delay                    | 88 |

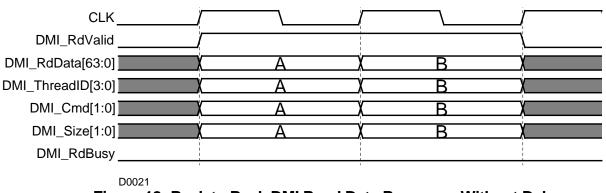

| Figure 18: | Back to Back DMI Read Data Response Without Delay                | 88 |

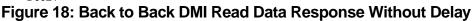

| Figure 19: | Back to Back DMI Read Data Response With Busy Delay              | 88 |

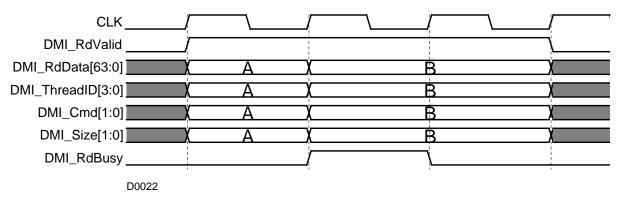

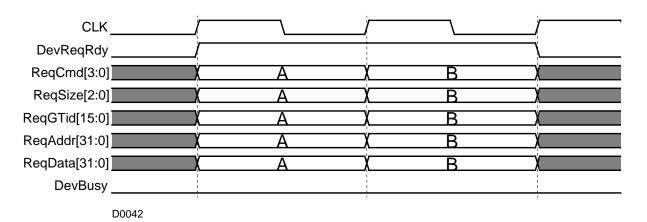

| Figure 20: | Single Request Enqueue                                           |    |

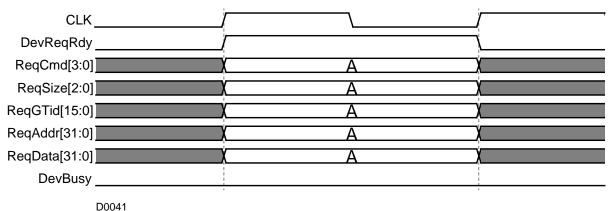

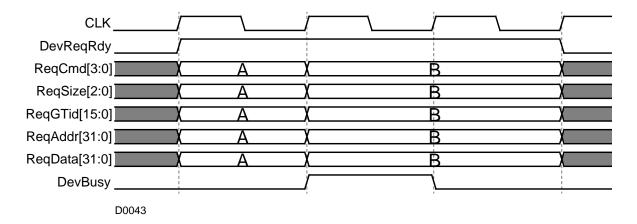

| Figure 21: | Back to Back Request Enqueue                                     | 90 |

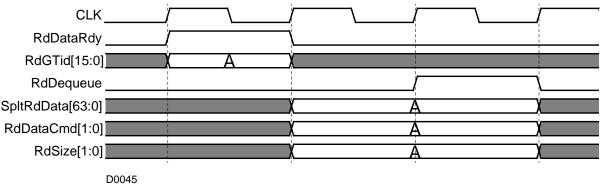

| Figure 23: | Single Split Read Return                                         | 92 |

| Figure 24: | RdDequeue Delay                                                  | 92 |

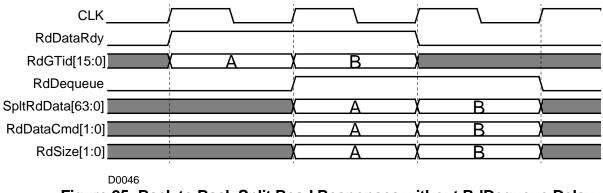

| Figure 25: | Back to Back Split Read Responses without RdDequeue Delay        |    |

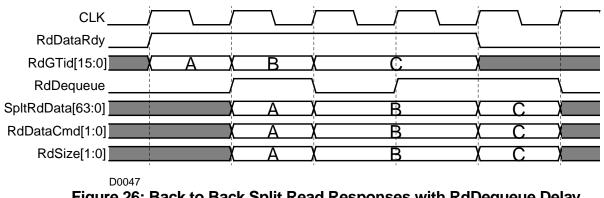

| Figure 26: | Back to Back Split Read Responses with RdDequeue Delay           | 93 |

| Figure 27: | Organization of the Block Transfer Controller                    |    |

# 1. NetVortex Product Overview

#### 1.1. Introduction

EXE/

This data sheet describes NetVortex, a scalable, multi-processor architecture developed specifically for use in network communications systems. NetVortex employs Lexra's LX8000 processor, and incorporates significant architectural features to support emerging network communications applications. A multi-processor IC based on NetVortex can perform IP routing and classification tasks at data rates up to OC-192 (30M packets/second).

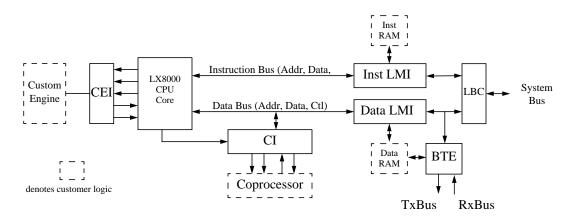

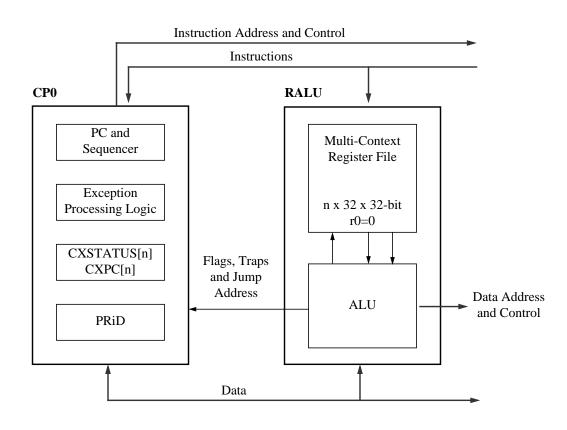

The LX8000 is based on Lexra's LX4189 processor, a complete MIPS R3000-class processor subsystem developed for ease of integration (See Figure 1 on page 13). The major subsystems are: the CPU core, Local Memory Interfaces (LMI) and LBus Controller (LBC). The technology includes an optional interface to a customer-defined Coprocessor (CI2) and optional customer extensions to the MIPS ISA (Custom Engine). The local instruction memories and data memories may include caches and fixed RAM; the sizes are configurable. The figure also highlights the LX8000 multi-context register file to support fast context switching. Additional LX8000 extensions include new bit-field operations for efficient packet header processing, and a Block Transfer Engine (BTE) attached to a dedicated RAM port, that is used in NetVortex for background data transfers.

Network communications systems are characterized by demanding, real-time performance requirements. Typically, system designers have addressed these requirements with custom ASICs, off-the-shelf processors, and PLDs. The explosive growth in the size and bandwidth of the Internet has recently stimulated semiconductor companies to develop a new type of product, called a Network Processor Unit (NPU), to serve these applications. These ICs incorporate multiple programmable cores and specialized peripherals. Compared to ASIC development, NPUs offer the system designer faster time-to-market and flexibility to implement differentiated services in software; compared to general-purpose, off-the-shelf components, NPUs offer the promise of lower cost and superior performance through architectural specialization. NetVortex is a scalable multi-processor with the specialized architectural features needed for high-performance packet processing for a wide variety of new products.

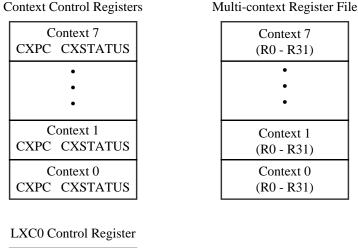

The time required to process packets for IP routing and classification is dominated by long latency operations, such as table lookups from large memories and buffer accesses. However, a distinguishing feature of network communications systems is that subsequent packets are readily available for independent processing. Therefore, a fast context switch can be exploited to hide the memory latency. NetVortex includes a configurable number (1-8) of general register sets and program counters, along with instructions for fast context switching. This enables multiple software threads to efficiently execute on a single processor. A thread is de-activated under software control either (i) unconditionally, (ii) when a load with context switch instruction is coded for a long latency load, or (iii) when a command is written to a shared system device.

Following a context switch, the CPU activates a new thread from the pool of ready threads. The context switch does not introduce stall cycles. Because the new thread has an independent general register set, it can quickly resume processing. To avoid stalling the new thread while the previous thread's data transfer completes, the LX8000 incorporates a Block Transfer Engine (BTE) connected to each processor's data memory for the transfer of packet data. In addition, the memory system is non-blocking, permitting local accesses and cache hits to operate in parallel with one outstanding global access per context. With this architecture, context switches may be used frequently to achieve optimal performance.

Packet processing also requires frequent access to bit-fields in the packet header that are not byte-aligned. For this reason, NetVortex has extended the MIPS Instruction Set Architecture (ISA) to include a complete set of bit-field operations for field extract, insert, set and clear. Deterministic allocation of real-time is another important problem in network communications software. This problem is compounded by multi-processing. For this reason, the LX8000's configuration options include dedicated (uncached) local instruction and data memories for real-time critical instructions and data in order to avoid cache miss penalties.

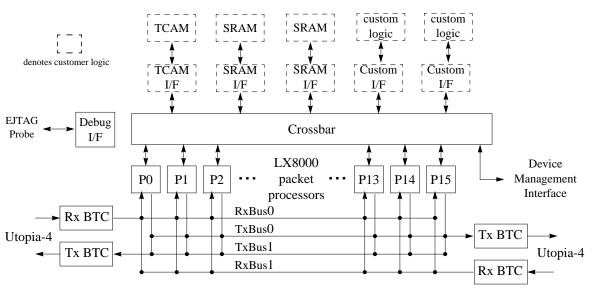

A typical system design based on NetVortex is illustrated in Figure 2 on page 14, which shows 16 processors, that include local instruction and data storage (not shown). A high bandwidth crossbar connects the processors to shared devices such as TCAMs, SRAMs, and custom logic. A Device Management Interface allows an application-specific management processor to access the shared devices.

NetVortex provides two optional peripherals: the Test and Set Engine and the Block Transfer Controller. The Test and Set Engine attaches to the crossbar and supports up to 32 unique semaphores. These semaphores may be used to control access to resources shared among any of the processors and contexts that have access to the semaphores. The Block Transfer Controller is connected to a dedicated port of each processor's data memory and transfers packet data over dedicated busses to external ports. IC designs using NetVortex can cost-effectively support a wide spectrum of network communications systems.

NetVortex employs Lexra's LX8000 packet processor, which is an extension Lexra's LX4189 processor. The LX8000 incorporates the LX4189's 6-stage RISC pipeline. As a result NetVortex can achieve high system clock performance in a portable cell-based design. The 6-stage pipeline also decouples customer-configurable RAMs from critical paths internal to the core.

Because the LX8000 packet processor executes the MIPS I instruction set<sup>1</sup>, a wide variety of third party software tools are available including compilers, operating systems, debuggers and in-circuit emulators. Lexra also supplies assembler extensions and a cycle accurate Instruction Set Simulator (ISS). Programmers may use "off-the-shelf" C compilers for initial coding, then replace performance critical code with optimized assembler code.

This data sheet describes the base LX4189 processor as well as LX8000 extensions to the LX4189. The remaining sections of this data sheet describe: hardware and instructions that support context switching (Section 2); the general RISC programming model (Section 3); LX8000 instruction extensions, including instructions for context switch, and bit-field processing (Section 4); processor memory interfaces (Section 5); coprocessor interfaces (Section 6); embedded debug support (Section 7); the NetVortex crossbar interconnect between processors and shared devices, and the device interface protocol. (Section 8); the optional NetVortex Test and Set Engine (Section 9); and the optional NetVortex Block Transfer Controller (Section 10)

#### 1.2. Key Features

- Complete Packet Processor Subsystem

- Executes MIPS I ISA (except unaligned loads, stores).

- Extensive third-party tool support.

- High-performance 6-stage pipeline.

- Local instruction memory, configurable sizes.

- Local data memory, configurable sizes.

- Memory interface logic included.

- Crossbar interface to access system devices.